Questões de Concurso

Sobre álgebra booleana e circuitos lógicos em engenharia eletrônica em engenharia eletrônica

Foram encontradas 503 questões

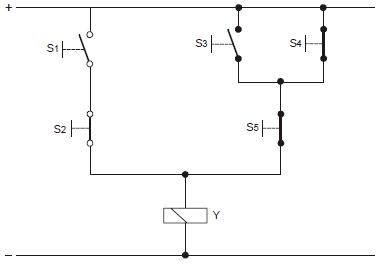

A função booleana da válvula: V = f (C1 , C2 , C3 ) é dada por

A expressão simplificada de Y é

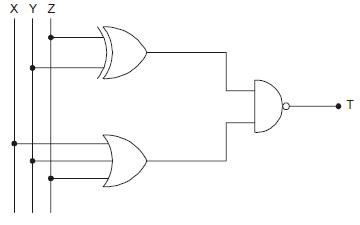

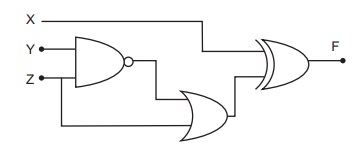

O circuito lógico combinacional mostrado na figura acima tem, como entradas, as variáveis lógicas X, Y e Z e, como saída, a variável F. A expressão simplificada da função booleana F é

O circuito acima representa uma porta lógica digital

implementada com a tecnologia NMOS. Os transistores de

chaveamento (com entradas

) são idênticos e do tipo

) são idênticos e do tipoenriquecimento, mas o transistor de carga é do tipo depleção. As

tensões de limiar dos transistores de chaveamento e carga são 1 V

e !3 V, respectivamente. Para esse circuito, o nível lógico alto (1

digital) é definido como qualquer tensão analógica compreendida

entre 3,5 V e 5 V, e o nível lógico baixo (0 digital) corresponde às

tensões analógicas entre 0 e 1,8 V. Esse circuito apresenta duas

peculiaridades:

I se pelo menos um dos transistores de chaveamento operar com

entrada em 5 V, a tensão de saída

não excederá 0,3 V;

não excederá 0,3 V;II somente com ambas as entradas simultaneamente no nível

lógico baixo, a saída atinge o nível lógico alto.

Com base nessas informações, julgue os itens subsequentes.

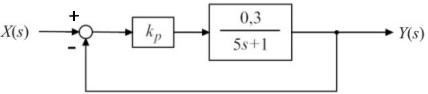

, no SI. Deseja-se implementar um controlador proporcional para esse sistema, segundo o diagrama de blocos mostrado abaixo, em que X(s) e Y(s) representam a transformada de Laplace da entrada e da saída do sistema em malha fechada, respectivamente, e kp é o ganho

, no SI. Deseja-se implementar um controlador proporcional para esse sistema, segundo o diagrama de blocos mostrado abaixo, em que X(s) e Y(s) representam a transformada de Laplace da entrada e da saída do sistema em malha fechada, respectivamente, e kp é o ganho

Considerando essas informações, assinale a opção que apresenta o valor do ganho kp de forma que a constante de tempo em malha fechada, no diagrama mostrado, seja de meio segundo.

As portas CMOS utilizam transistores PMOS em combinação com transistores NMOS. Como esses dois tipos de transistores possuem características diferentes, é comum que os transistores PMOS e NMOS tenham dimensões distintas, de forma a compensar efeitos dessa diferença.

A tabela acima mostra a tabela verdade de um circuito

combinacional com entradas A, B, C e D, e saída S. Com relação a

esse circuito, julgue os itens subsequentes.

A tabela acima mostra a tabela verdade de um circuito

combinacional com entradas A, B, C e D, e saída S. Com relação a

esse circuito, julgue os itens subsequentes.