Questões de Concurso

Sobre eletrônica analógica na engenharia eletrônica em engenharia eletrônica

Foram encontradas 777 questões

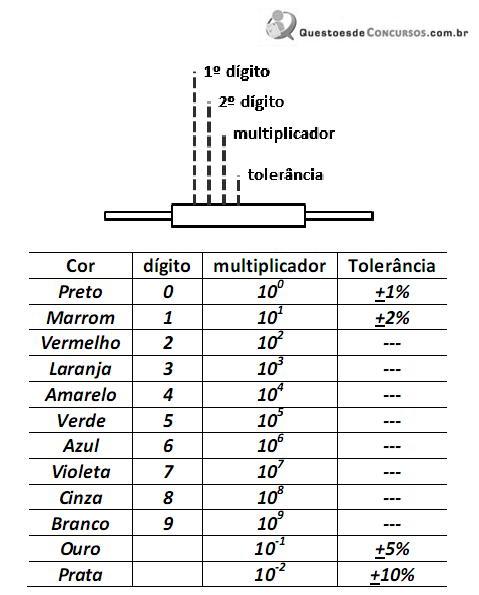

Para uma combinação de cores, onde o 1º dígito é vermelho, o 2º dígito é verde, o multiplicador é laranja e a tolerância é ouro, o resistor possui uma resistência de

I. Por questão de velocidade de resposta, deve-se evitar o uso de módulos de entrada que possuem acoplamento óptico para entrada de sinais digitais.

II. Os módulos de saída analógica com saída do tipo corrente geralmente fornecem correntes de 0 mA a 20 mA ou 4 mA a 20 mA.

III. Os módulos de saída que necessitam operar a velocidades maiores devem utilizar elementos de chaveamento do tipo relé.

IV. Existem módulos de saída especiais que podem fornecer sinais do tipo PWM.

Está correto o que se afirma APENAS em

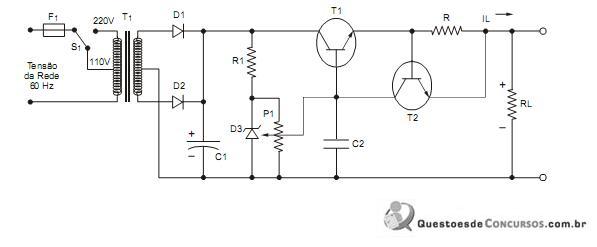

I. D1 e D2, juntos formam um retificador de meia onda.

II. A tensão de saída é ajustável.

III. C2 e T2 formam um filtro ativo de saída.

IV. Apresenta um retificador de onda completa em ponte.

V. Apresenta um limitador de corrente.

VI. T1 atua como um drive de corrente.

VII. R1, D3 e P1 formam um estabilizador ajustável de tensão.

Está correto o que se afirma APENAS em

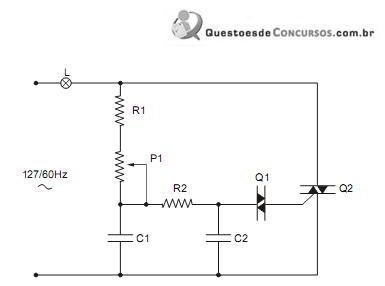

Os componentes Q1 e Q2 são, respectivamente,

Se um sinal cossenoidal de duração infinita e com frequência de 10 Hz for multiplicado por outro sinal cossenoidal de duração infinita e com frequência de 1 MHz, então a transformada de Fourier (ou espectro de frequência) do sinal resultante dessa multiplicação terá uma função impulso na frequência de –1,01 MHz e outra em +1,01 MHz e será igual a zero em qualquer outra frequência.

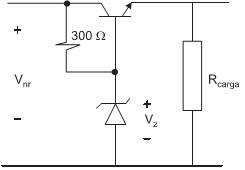

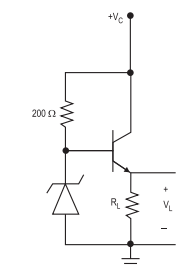

O circuito da figura acima é uma fonte de tensão regulada que usa como referência um diodo zener com 6 V de tensão nominal. A tensão não regulada de entrada (Vnr ) tem valor nominal de 15 V e admite uma variação de ± 20% em torno do seu valor nominal. A resistência de carga pode assumir valores que variam de 100 Ω até a resistência infinita (ckt aberto).

Nessas condições, qual será a corrente máxima, em mA, suportada pelo diodo?

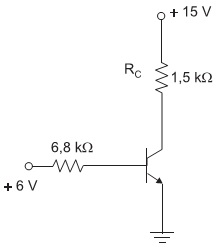

O circuito da figura usa um transistor NPN (ß = 100 e VBE = 0,6 V).

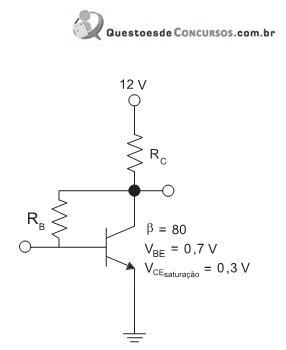

Analisando as condições e os dados do circuito, conclui-se que o transistor está saturado e o valor aproximado da potência dissipada no resistor RC, em mW, é

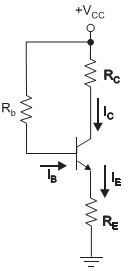

O tipo de configuração montada com o transistor mostrada na figura acima corresponde ao tipo de polarização conhecido por

O ganho desse amplificador, em dB, é

Dado: Considere o log10 (2) = 0,3

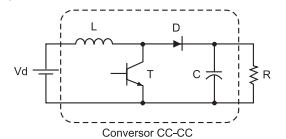

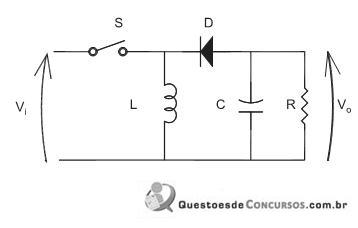

O circuito mostrado na figura acima, em especial a parte limitada pelo quadro pontilhado, é um conversor CC-CC do tipo

No circuito eletrônico da figura acima, todos os componentes são considerados ideais. O transistor opera com ganho β = 20 e V BE= 0,6 V. Sabe-se que o diodo Zener opera com tensão nominal de 6 V, que o circuito deve funcionar com a tensão VC podendo assumir valores entre 15 e 30 V e que a resistência de carga RL é incerta, podendo variar de 5 Ω até infinito (circuito sem carga). O projeto prevê que a tensão V L , com alguma tolerância, permaneça constante. Nesse contexto, o diodo Zener deverá ser especificado no projeto para suportar uma potência máxima, em W, de

A figura acima apresenta um conversor buck boost, que opera com modulação por largura de pulso, onde o duty cycle D = 0,6. Para uma entrada DC Vi = 15 V e considerando o funcionamento do circuito em regime permanente, o valor médio da tensão de saída Vo, em volts, é

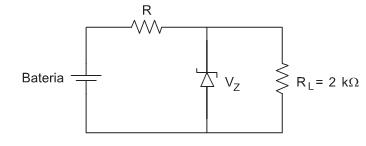

No circuito da figura acima, os valores de R e da tensão nominal do diodo zener, Vz, são desconhecidos. Para determiná-los, utilizaram-se duas baterias diferentes, verificando-se as potências dissipadas pelos resistores.

Os valores obtidos estão na tabela abaixo.

Bateria PR PRL 10 V 12 mW 8 mW 18 V 48 mW 18 mW

Com base nos dados acima apresentados, os valores de R e Vz são, respectivamente,

O circuito da figura acima mostra os dados de polarização de um transistor NPN. Para que a corrente CC de coletor seja de 2 mA e seja garantida uma excursão, no sinal de coletor, de 2 V (pico a pico), alcançando-se o limiar de transição para a região de saturação do transistor, os valores de RB e RC são, em kΩ respectivamente,

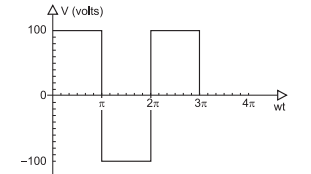

Considere um conversor CA-CC monofásico, de onda completa e retificado a diodo. Esse conversor é alimentado por um outro conversor monofásico CC-CA, cuja tensão de saída é uma onda quadrada, de frequência 60 Hz, mostrada na figura acima. Supondo-se que os dois conversores são considerados ideais, o valor da potência média, em watts, dissipada em uma resistência de 10 Ω conectada no lado CC do retificador, é

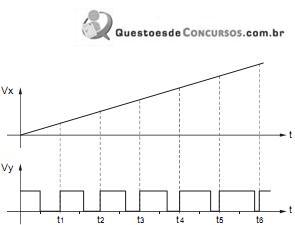

O sinal Vy é do tipo