Questões de Concurso

Sobre eletrônica digital na engenharia eletrônica em engenharia eletrônica

Foram encontradas 888 questões

PORQUE

A estação terminal remota é um dispositivo eletrônico controlado por microprocessador que possui, além de outros componentes, conversores A/D e portas de comunicação.

Analisando-se as afirmações acima, conclui-se que

A figura acima, na forma de blocos, mostra o esquema básico de

uma read only memory (ROM) genérica.

A partir dessas informações, julgue os itens que se seguem.

A figura acima, na forma de blocos, mostra o esquema básico de

uma read only memory (ROM) genérica.

A partir dessas informações, julgue os itens que se seguem.

A figura acima, na forma de blocos, mostra o esquema básico de

uma read only memory (ROM) genérica.

A partir dessas informações, julgue os itens que se seguem.

A figura acima mostra um Flip-Flop do tipo JK mestre-escravo

com entrada preset (PR) e clear (CLR). Considerando essas

informações, julgue os itens seguintes.

A figura acima mostra um Flip-Flop do tipo JK mestre-escravo

com entrada preset (PR) e clear (CLR). Considerando essas

informações, julgue os itens seguintes.

A figura acima mostra um Flip-Flop do tipo JK mestre-escravo

com entrada preset (PR) e clear (CLR). Considerando essas

informações, julgue os itens seguintes.

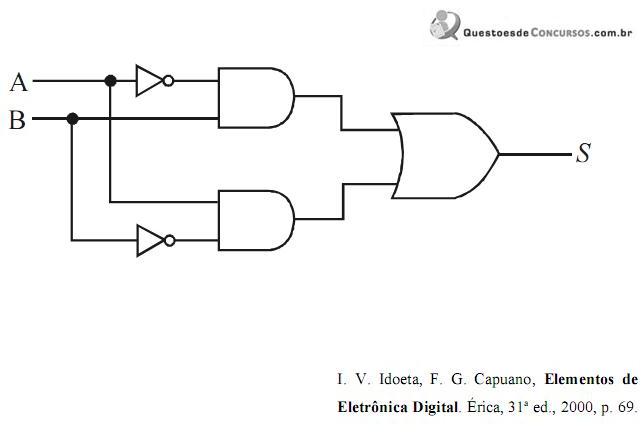

Tendo como base o circuito lógico mostrado na figura acima, e

considerando os sinais aplicados às entradas A e B, julgue os

itens que se seguem.

Tendo como base o circuito lógico mostrado na figura acima, e

considerando os sinais aplicados às entradas A e B, julgue os

itens que se seguem.

A respeito do circuito lógico acima, julgue o item a seguir.

A respeito do circuito lógico acima, julgue o item a seguir.A expressão booleana resultante para a saída S é S=A.B.

Considerando a tabela-verdade acima, que descreve o

comportamento de um circuito convencional com três

entradas e uma saída, e na qual X representa dont’care

(não importa), julgue os itens seguintes.

Considerando a tabela-verdade acima, que descreve o

comportamento de um circuito convencional com três

entradas e uma saída, e na qual X representa dont’care

(não importa), julgue os itens seguintes.

Considerando a tabela-verdade acima, que descreve o

comportamento de um circuito convencional com três

entradas e uma saída, e na qual X representa dont’care

(não importa), julgue os itens seguintes.

Considerando a tabela-verdade acima, que descreve o

comportamento de um circuito convencional com três

entradas e uma saída, e na qual X representa dont’care

(não importa), julgue os itens seguintes.

Considerando a tabela-verdade acima, que descreve o

comportamento de um circuito convencional com três

entradas e uma saída, e na qual X representa dont’care

(não importa), julgue os itens seguintes.

Um encoder incremental possui dois sinais de saída, na forma de onda

quadrada, de mesma freqüência e defasados em ¼ de ciclo. Assumindo que

as saídas dos canais tenham ciclo de trabalho de 50%, existem duas

possibilidades para a temporização dos mesmos, conforme indicado por caso

A e caso B na figura acima. Os sinais do encoder incremental são

processados pelo circuito digital indicado na mesma figura. Acerca do

funcionamento desse circuito em regime permanente, e considerando que

todos os componentes do circuito são ideais, julgue os itens subseqüentes.

do Flip-flop do tipo D sempre estará em nível lógico baixo.

do Flip-flop do tipo D sempre estará em nível lógico baixo.

Um encoder incremental possui dois sinais de saída, na forma de onda

quadrada, de mesma freqüência e defasados em ¼ de ciclo. Assumindo que

as saídas dos canais tenham ciclo de trabalho de 50%, existem duas

possibilidades para a temporização dos mesmos, conforme indicado por caso

A e caso B na figura acima. Os sinais do encoder incremental são

processados pelo circuito digital indicado na mesma figura. Acerca do

funcionamento desse circuito em regime permanente, e considerando que

todos os componentes do circuito são ideais, julgue os itens subseqüentes.

sempre estará em nível alto.

sempre estará em nível alto.