Questões de Engenharia Eletrônica para Concurso

Foram encontradas 3.780 questões

Acerca do circuito digital com entradas lógicas A, B, C e D mostrado acima e considerando que a notação X’ represente a negação da variável booleana X, julgue o item.

O circuito mostrado é classificado como sequencial por

apresentar elementos de memória.

Acerca do circuito digital com entradas lógicas A, B, C e D mostrado acima e considerando que a notação X’ represente a negação da variável booleana X, julgue o item.

A saída do circuito pode ser descrita, na forma normal

canônica conjuntiva, pela equação F = AD + B’D.

Acerca do circuito digital com entradas lógicas A, B, C e D mostrado acima e considerando que a notação X’ represente a negação da variável booleana X, julgue o item.

A saída F do circuito pode ser descrita pela equação F = D(A+B’).

No que se refere aos conceitos de eletrônica analógica, julgue o item.

Fontes de tensão chaveadas regulam a tensão e a corrente de saída, chaveando elementos de armazenamento de energia (capacitores e indutores). Apresentam a vantagem de serem mais eficientes e fisicamente mais compactas que as fontes de tensão lineares.

No que se refere aos conceitos de eletrônica analógica, julgue o item.

Transistores MOS são menos sensíveis a descargas eletrostáticas que transistores bipolares de junção.

No que se refere aos conceitos de eletrônica analógica, julgue o item.

Em um amplificador‐fonte comum, o uso de uma resistência de degeneração de fonte causa diminuição do ganho do circuito.

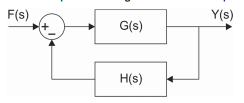

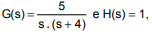

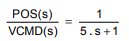

Um sistema de controle automático de velocidade possui o diagrama de blocos apresentado na ilustração abaixo.

Admitindo que  a expressão da função de transferência

a expressão da função de transferência  será

será

Nesse sistema, quando aplica-se um degrau de 0,0 a 100,0 [%]em VCMD, o tempo necessário para que o pistão alcance mais de 95,0% em sua posição POS é, em [s], de, aproximadamente,

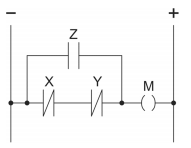

Em posse de tais informações, a expressão lógica equivalente de M será

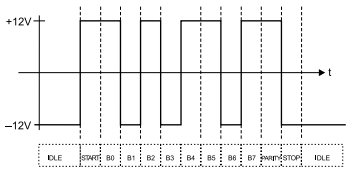

A seguinte figura apresenta os sinais do protocolo de comunicação serial assíncrona utilizado no RS-232.

A eficiência máxima desse protocolo é, aproximadamente, de

Um determinado comportamento de um circuito lógico foi especificado com linguagens de descrição de hardware (HDL). Após o processo de síntese de alto nível, ferramentas computacionais determinaram um fluxo de dados (data path) e um fluxo de controle e estados (control path), usando RTL (register transfer logic), IP (intelectual property) Cores e outros recursos tecnológicos disponíveis em uma determinada arquitetura de FPGA. Foi realizada uma simulação digital pós-síntese que verificou que os resultados atenderam à especificação original. Entretanto, após a programação, o hardware real da FPGA não operou de forma correta, com falhas durante seu funcionamento.

A respeito desse processo, é correto afirmar que