Questões de Concurso

Sobre flip-flops em engenharia eletrônica

Foram encontradas 112 questões

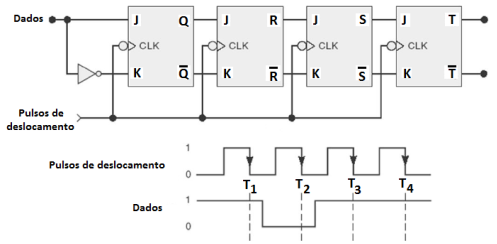

A figura a seguir mostra uma transferência serial de dados por meio de um registrador de deslocamento.

Assinale a opção que indica o diagrama de tempo para a saída S.

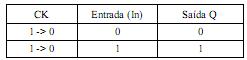

Considerando a figura apresentada, que ilustra um circuito lógico de um flip-flop RS com entrada CLOCK, julgue o item que se segue.

Caso o nível lógico da entrada clock seja 0, o estado de saída do flip-flop permanecerá inalterado, ainda que haja variações das entradas R e S.

Considerando a figura apresentada, que ilustra um circuito lógico de um flip-flop RS com entrada CLOCK, julgue o item que se segue.

Se o nível lógico do CLOCK for 1, então o circuito se

comportará como um flip-flop JK.

A denominação do circuito integrado 74LS373, de acordo com os fabricantes, é 3-STATE Octal D-Type Transparent Latches and Edge-Triggered Flip-Flops.

Portanto, trata-se de um

(micro segundo) para o tempo de propagação, e que o contador deve contar 2

voltas, assinale a alternativa correta.

(micro segundo) para o tempo de propagação, e que o contador deve contar 2

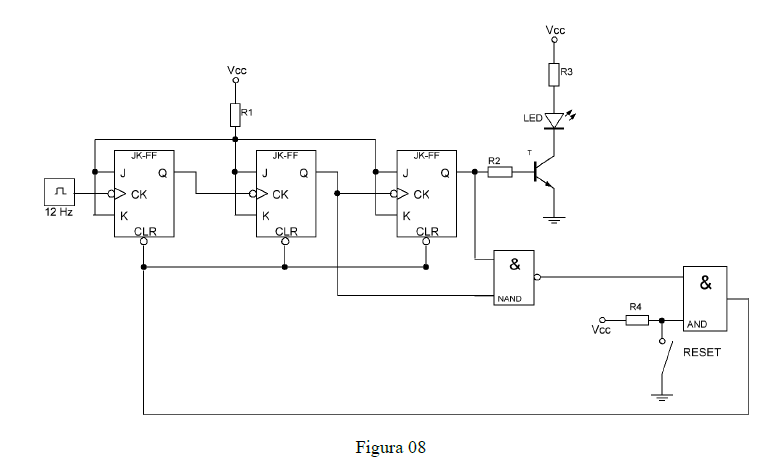

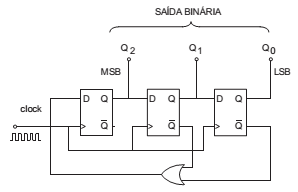

voltas, assinale a alternativa correta. O circuito abaixo trata de um gerador de sequência, em anel, implementado com Flip Flop tipo D e porta lógica.

A sequência de loop, em numeração decimal, executada pelo gerador, é o que consta em

Julgue o próximo item, acerca de sistemas digitais.

Um flip-flop S-R não pode ter, ao mesmo tempo, as entradas

S e R em nível alto.

MOV AH,20h

MOV AL,80h

ADD AL,AH

MOVSX AX,AL

ADD AL,AH

MOVZX AX,AL

Sabendo-se que a instrução MOVSX realiza uma cópia com extensão de sinal e a MOVZX realiza uma cópia com extensão de zeros, a execução do código listado acima faz com que AX termine com o valor

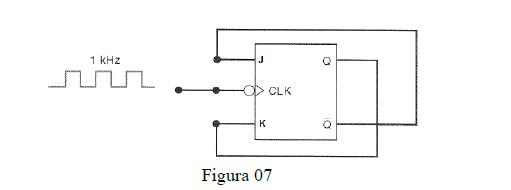

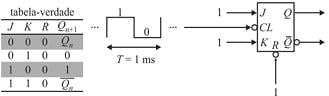

A figura abaixo ilustra um flip-flop JK mestre-escravo, em que J e K são os terminais de entrada; CL é a entrada de clock; R, o terminal de reset; e Q e

são os terminais de saída. O flip-flop obedece à tabela-verdade apresentada, na qual Qn+1e Qn são as saídas após o disparo do clock e antes desse disparo, respectivamente, e o clock é um trem de pulsos com nível adequado de amplitude e período T = 1 ms. Considerando essas informações, é correto afirmar que a saída Q do flip-flop alterna entre os níveis lógicos 1 e 0 a cada 1 ms.

são os terminais de saída. O flip-flop obedece à tabela-verdade apresentada, na qual Qn+1e Qn são as saídas após o disparo do clock e antes desse disparo, respectivamente, e o clock é um trem de pulsos com nível adequado de amplitude e período T = 1 ms. Considerando essas informações, é correto afirmar que a saída Q do flip-flop alterna entre os níveis lógicos 1 e 0 a cada 1 ms.

Biestáveis, ou flip-flops, são elementos básicos dos circuitos sequenciais

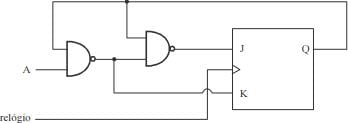

J = A .

.

.Considerando que, no circuito lógico mostrado na figura acima, o flip-flop seja do tipo JK mestre-escravo, julgue o item a seguir.

Se A = 1, então o estado de Q será mantido após um ciclo

completo de relógio.

Considerando que, no circuito lógico mostrado na figura acima, o flip-flop seja do tipo JK mestre-escravo, julgue o item a seguir.

J = A . Q +