Questões de Concurso

Sobre flip-flops em engenharia eletrônica

Foram encontradas 111 questões

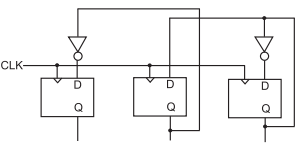

No circuito da figura acima, considere que os flip-flops começam zerados após a energização do sistema. O número de estados que se repetem indefinidamente na

sequência permanente é

Com relação a sistemas e dispositivos digitais, julgue o item seguinte.

No flip-flop JK do tipo mestre-escravo, se as entradas J e K

estiverem todo o tempo conectadas ao nível lógico 1, então a

saída Q, após sucessivos ciclos de relógio, permanecerá no

nível lógico 1.

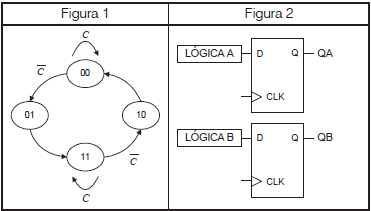

A Figura 1, acima, mostra um diagrama de quatro estados definidos pelos bits B e A, sendo B o mais significativo, e pelo bit de controle C.

A Figura 2, por sua vez, mostra uma implementação síncrona desse diagrama de estados com o uso de flip-flops D e das lógicas A e B.

Estas lógicas devem ser, respectivamente:

Contador Flip-Flop JK

A figura acima mostra um contador binário conectado a um flip-flop JK, ambos com entrada de clock acionada por borda. O contador está programado para decrementar (D/U = 1) e, no início da contagem, Q = Q1 = Q0 = 0, sendo Q1 mais significativo do que Q0. Além disso, cada pulso de clock do contador (Clk1) é seguido por um pulso de clock do flip-flop (Clk2), havendo tempo suficiente para a estabilização das saídas de ambos os dispositivos.

de componentes conectados para processar informação em forma

digital. Os componentes básicos utilizados na construção de

sistemas digitais são dispositivos eletrônicos que vão de circuitos

biestáveis a computadores completos. As ligações entre esses

componentes eletrônicos são conexões físicas, por meio das quais

a informação digital pode ser transmitida. O número de

elementos pode chegar a milhares de componentes. Quanto mais

componentes são necessários para a realização de um sistema

digital, mais complexo ele é e mais difícil se torna entender seu

funcionamento ou projetá-lo.

A partir do texto acima, julgue os itens subsequentes.

de componentes conectados para processar informação em forma

digital. Os componentes básicos utilizados na construção de

sistemas digitais são dispositivos eletrônicos que vão de circuitos

biestáveis a computadores completos. As ligações entre esses

componentes eletrônicos são conexões físicas, por meio das quais

a informação digital pode ser transmitida. O número de

elementos pode chegar a milhares de componentes. Quanto mais

componentes são necessários para a realização de um sistema

digital, mais complexo ele é e mais difícil se torna entender seu

funcionamento ou projetá-lo.

A partir do texto acima, julgue os itens subsequentes.

A figura acima representa um flip-flop RS básico, construído a

partir de portas NÃO-E (NE) e inversores. No circuito, as

variáveis de entrada são S e R e Q representa a saída anterior

à aplicação das entradas.

Considerando essas informações, julgue os itens que se seguem.

A figura acima representa um flip-flop RS básico, construído a

partir de portas NÃO-E (NE) e inversores. No circuito, as

variáveis de entrada são S e R e Q representa a saída anterior

à aplicação das entradas.

Considerando essas informações, julgue os itens que se seguem.

Considerando a figura acima, que mostra o diagrama lógico de

uma célula de memória RAM construída a partir de flip-flop,

julgue os itens subsequentes.

Considerando a figura acima, que mostra o diagrama lógico de

uma célula de memória RAM construída a partir de flip-flop,

julgue os itens subsequentes.

A figura acima mostra um Flip-Flop do tipo JK mestre-escravo

com entrada preset (PR) e clear (CLR). Considerando essas

informações, julgue os itens seguintes.