Questões de Concurso

Sobre flip-flops em engenharia eletrônica

Foram encontradas 111 questões

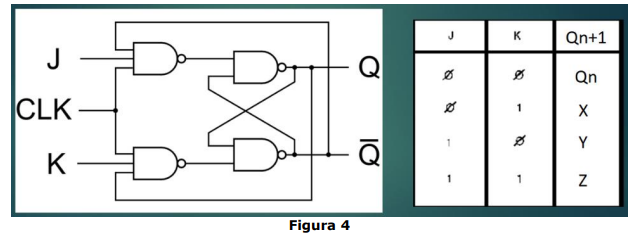

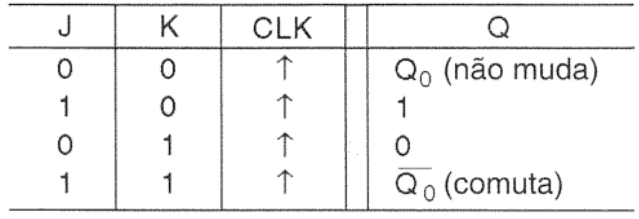

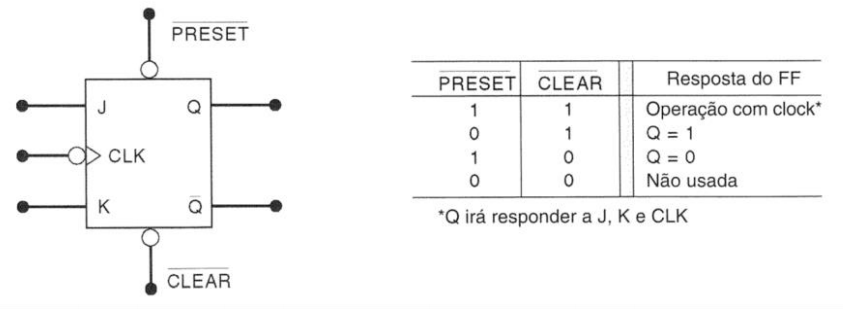

A Figura 4 apresenta um circuito digital conhecido como flip-flop JK, amplamente aplicado em projetos e circuitos digitais sequenciais, tais como contadores e registradores. Assinale a alternativa que substitui adequadamente as letras X, Y e Z presentes na tabela-verdade do flip-flop JK abaixo, na coluna Qn+1, que representa o próximo estado lógico na saída Qn após o pulso de clock.

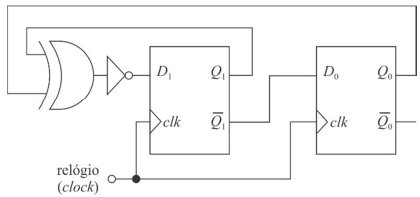

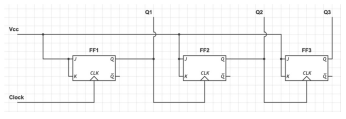

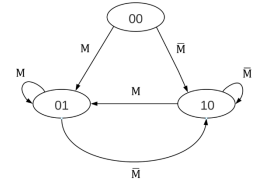

A figura precedente representa um circuito sequencial com 2 bits, que utiliza flip-flops do tipo D, gatilhados por borda de subida. A sequência é iniciada por ação de um circuito de reset não explicitado na figura, a partir do estado D1D0 = 00.

Tendo como referência essas informações, julgue o item seguinte, a respeito de eletrônica digital.

O circuito sequencial representado na figura realiza uma

contagem de forma cíclica, repetindo a sequência 00 01 10 11.

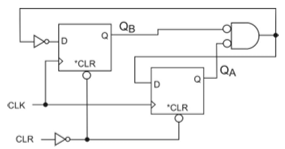

A lógica de menor soma de produtos a ser usada para acionar DB é

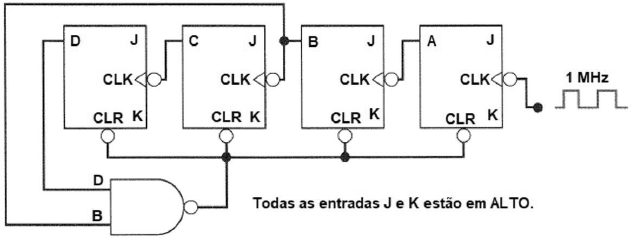

Após um pulso de CLR em nível baixo e mais de 30 pulsos de CLK, sem que ocorra novo pulso de CLR, o estado QBQA do circuito da figura acima, composto por dois flip-flops, dois inversores e mais uma porta lógica, ficará

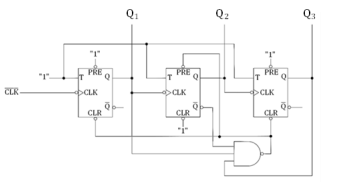

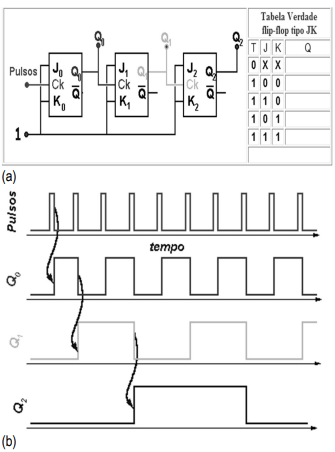

Se a frequência da variável Clock do diagrama da figura precedente for igual a 160 kHz, então as frequências de Q1, Q2 e Q3 serão, respectivamente, iguais a

Com relação à tecnologia de empacotamento em módulos de multi-chip (MCM), julgue o item seguinte.

Em um MCM, vários componentes são montados em

substratos diferentes e conectados por meio de ligação de fita

ou por ligação tipo flip-chip.

O empacotamento do tipo CBGA é o de maior custo efetivo entre os tipos de empacotamento BGA e possui entre 300 e 600 contatos ou terminais de entrada e saída.

Na verificação física de sistemas VLSI em modo misto, a integridade do sinal e as considerações de ruído são menos críticas para circuitos analógicos que para circuitos digitais, tornando o roteamento e a disposição dos componentes analógicos menos importantes no processo de design.

O flip-flop tipo D pode ser implementado a partir de um flip-flop J-K.

Julgue o item seguinte, relativos à eletrônica digital.

Em registradores, a entrada de clock é utilizada quando se

deseja realizar uma transferência de dados síncrona.

Podemos afirmar que quando: J =0 , K = 0, clock =

Podemos afirmar que quando: J =0 , K = 0, clock =  , a saída Q será :

, a saída Q será :

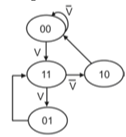

Esse contador possui a seguinte quantidade de estados estáveis:

Dado que o bit B2 será implementado utilizando um flip-flop D, a sua lógica de próximo estado pode ser expressa por

Esse circuito opera com flip-flop e é denominado

de um flip-flop D possui nível lógico

constante e igual a zero se o SLQR ³cleaU´ do

dispositivo é acionado por lógica complementar

e está conectado a um sinal de nível lógico alto.

de um flip-flop D possui nível lógico

constante e igual a zero se o SLQR ³cleaU´ do

dispositivo é acionado por lógica complementar

e está conectado a um sinal de nível lógico alto. Assinale a alternativa correta

Analise o circuito a seguir.

Após análise desse circuito, a função implementada é de um

Flip-flop é um circuito digital pulsado (uso de clock) utilizado como uma memória de um bit. Com relação ao assunto, identifique como verdadeiras (V) ou falsas (F) as seguintes afirmativas:

( ) A tabela verdade de um flip-flop J-K com clock é a seguinte:

( ) O flip-flop disparado por transição faz uso de um detector de transição para garantir que a saída vai responder à entrada somente quando uma transição de disparo do sinal de clock ocorrer. Caso esse detector não seja utilizado, o circuito resultante vai operar como um latch do tipo C.

( ) A tabela verdade de um flip-flop assíncrono JCLK é a apresentada abaixo:

( ) Os atrasos de propagação ocorrem sempre que um sinal causa a mudança de estado da saída de um flip-flop.

Assinale a alternativa que apresenta a sequência correta, de cima para baixo