Questões de Concurso

Sobre transistor em engenharia eletrônica

Foram encontradas 349 questões

integrados digitais, julgue itens subsecutivos.

integrados digitais, julgue itens subsecutivos.

Considere o diagrama acima, que representa um amplificador, com

transistor bipolar de junção que está polarizado corretamente na

região ativa, e cujo ganho

é igual a 20. Considere,

é igual a 20. Considere, ainda, que

seja igual a 12 V e que o potencial CC de

seja igual a 12 V e que o potencial CC depolarização seja igual a 4 V no emissor e igual a 8 V no coletor.

Considere, por fim, que todos os capacitores tenham capacitância

alta o suficiente para que funcionem como curtos-circuitos para o

sinal

em razão da frequência desse sinal. Com base nessas

em razão da frequência desse sinal. Com base nessasinformações, julgue os itens seguintes.

for um sinal senoidal com amplitude de pico de 1 mV, então, a tensão no coletor do transistor será igual a soma de uma tensão contínua de 4 V e de uma tensão senoidal, que terá amplitude de pico igual a 20 mV e a mesma frequência e a mesma fase do sinal

for um sinal senoidal com amplitude de pico de 1 mV, então, a tensão no coletor do transistor será igual a soma de uma tensão contínua de 4 V e de uma tensão senoidal, que terá amplitude de pico igual a 20 mV e a mesma frequência e a mesma fase do sinal

Considere o diagrama acima, que representa um amplificador, com

transistor bipolar de junção que está polarizado corretamente na

região ativa, e cujo ganho

é igual a 20. Considere,

é igual a 20. Considere, ainda, que

seja igual a 12 V e que o potencial CC de

seja igual a 12 V e que o potencial CC depolarização seja igual a 4 V no emissor e igual a 8 V no coletor.

Considere, por fim, que todos os capacitores tenham capacitância

alta o suficiente para que funcionem como curtos-circuitos para o

sinal

em razão da frequência desse sinal. Com base nessas

em razão da frequência desse sinal. Com base nessasinformações, julgue os itens seguintes.

Considere o diagrama acima, que representa um amplificador, com

transistor bipolar de junção que está polarizado corretamente na

região ativa, e cujo ganho

é igual a 20. Considere,

é igual a 20. Considere, ainda, que

seja igual a 12 V e que o potencial CC de

seja igual a 12 V e que o potencial CC depolarização seja igual a 4 V no emissor e igual a 8 V no coletor.

Considere, por fim, que todos os capacitores tenham capacitância

alta o suficiente para que funcionem como curtos-circuitos para o

sinal

em razão da frequência desse sinal. Com base nessas

em razão da frequência desse sinal. Com base nessasinformações, julgue os itens seguintes.

seja retirado do circuito, ocorrerá um aumento no ganho A do amplificador.

seja retirado do circuito, ocorrerá um aumento no ganho A do amplificador.

Considere o diagrama acima, que representa um amplificador, com

transistor bipolar de junção que está polarizado corretamente na

região ativa, e cujo ganho

é igual a 20. Considere,

é igual a 20. Considere, ainda, que

seja igual a 12 V e que o potencial CC de

seja igual a 12 V e que o potencial CC depolarização seja igual a 4 V no emissor e igual a 8 V no coletor.

Considere, por fim, que todos os capacitores tenham capacitância

alta o suficiente para que funcionem como curtos-circuitos para o

sinal

em razão da frequência desse sinal. Com base nessas

em razão da frequência desse sinal. Com base nessasinformações, julgue os itens seguintes.

melhora a estabilidade da polarização CC do circuito.

melhora a estabilidade da polarização CC do circuito.seguintes.

eletrônica digital, julgue os próximos itens.

Em um laboratório de eletrônica, foram realizadas

medições elétricas em um circuito de polarização de um transistor

bipolar de junção (TBJ) do tipo npn, representado na figura acima.

Os valores obtidos para a corrente de emissor e de base do

dispositivo foram 1,29 mA e 12,8 mA, respectivamente.

Com base nesses dados, julgue os itens a seguir.

Em um laboratório de eletrônica, foram realizadas

medições elétricas em um circuito de polarização de um transistor

bipolar de junção (TBJ) do tipo npn, representado na figura acima.

Os valores obtidos para a corrente de emissor e de base do

dispositivo foram 1,29 mA e 12,8 mA, respectivamente.

Com base nesses dados, julgue os itens a seguir.

Em um laboratório de eletrônica, foram realizadas

medições elétricas em um circuito de polarização de um transistor

bipolar de junção (TBJ) do tipo npn, representado na figura acima.

Os valores obtidos para a corrente de emissor e de base do

dispositivo foram 1,29 mA e 12,8 mA, respectivamente.

Com base nesses dados, julgue os itens a seguir.

corrente contínua (CC) ou alternada (CA). A conversão de uma

forma em outra é feita por meio de equipamentos conversores que

utilizam dispositivos semicondutores de chaveamento. Acerca desse

tema, julgue os itens subsequentes.

Acerca dos dispositivos eletrônicos, julgue o próximo item.

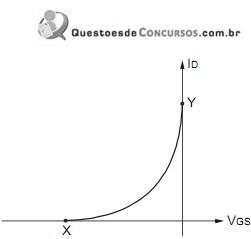

O transistor de unijunção (UJT) é um dispositivo de três

terminais. O silício pode ser utilizado na construção desse tipo

de componente.

Tais características são alcançadas pelo uso dos seguintes estágios amplificadores em série: